https://www.theinformation.com/articles/tsmc-make-ai-chips-fast-enough?eu=wlYhPpPQwn0NL5uNzxCQ6A&utm_source=ti_app&rc=01qtpq

AIチップではtsmcの製造とNVIDIAの設計ではどっちが難しいですか

とても本質的な質問です。結論から言うと👇

「難しさの“種類”が違うが、現在のAIチップでは

👉 技術的・構造的により“詰んでいる”のはTSMCの製造」

ただし

👉 価値創出・差別化の源泉として“代替不能”なのはNVIDIAの設計

という関係です。

結論を一文で

- 一番「真似できない」= NVIDIAの設計

- 一番「物理的に詰まっている」= TSMCの製造

① TSMCの製造は何がそんなに難しいのか

TSMC

難しさの本質:物理 × 組織 × 時間

TSMCがやっているのは「工場」ですが、普通の工場ではありません。

技術的に

- 3nm / 2nmという原子数個レベルの加工

- EUV露光(ASML製装置)前提

- 歩留まりが90%→85%になるだけで利益が吹き飛ぶ

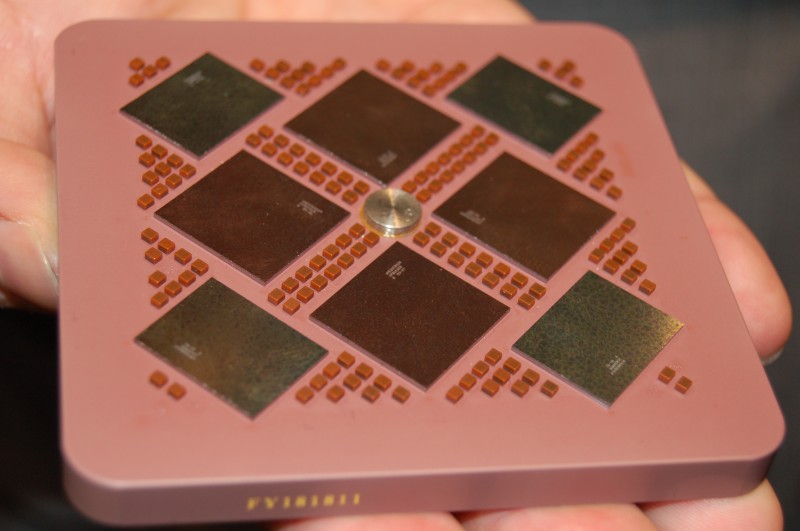

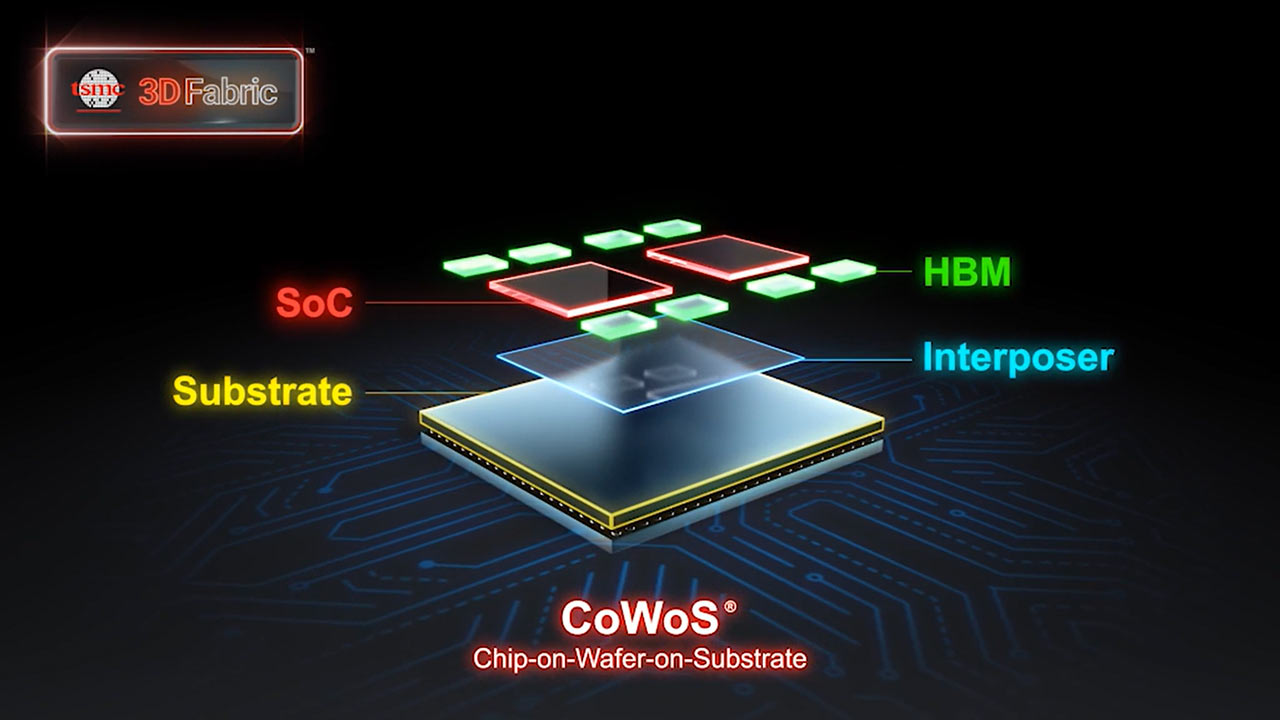

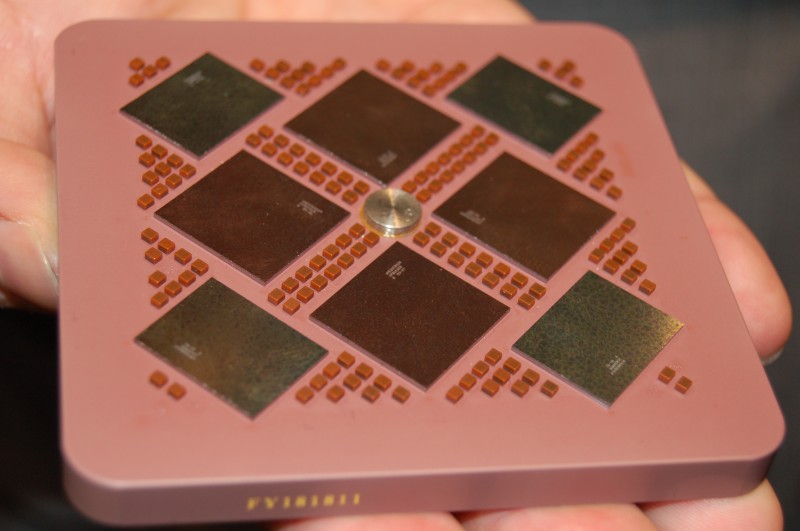

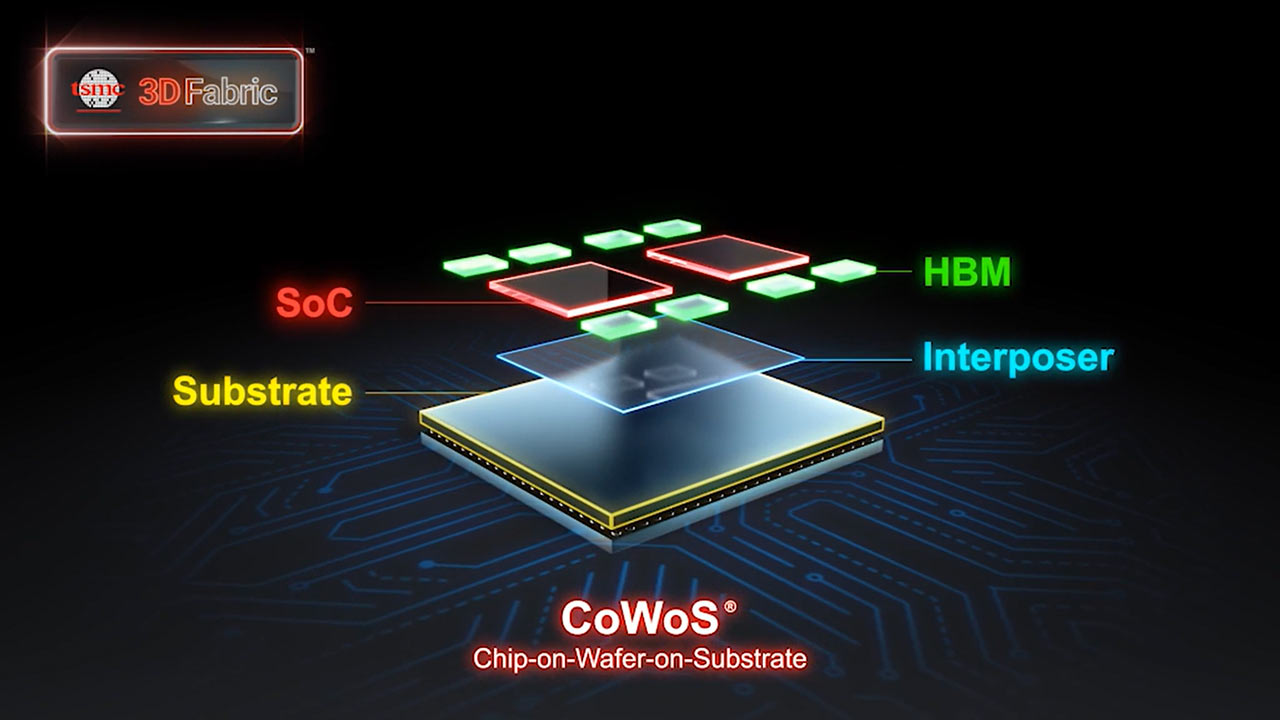

- CoWoSなど先端パッケージングが別ボトルネック

組織的に

- 数万人の熟練プロセス技術者

- 設計会社(NVIDIA, Apple等)と同時並行で最適化

- ノウハウは論文にならない「暗黙知」

時間的に

- 新Fab建設:5〜7年

- 設備投資:1兆円単位

- 今すぐ増産する手段がない

👉

需要が爆発しても、物理的に追いつけない

② NVIDIAの設計は何が難しいのか

NVIDIA

難しさの本質:知能 × 全体最適 × エコシステム

NVIDIAは「チップ設計会社」ですが、実態は👇

単なる回路設計ではない

- GPUアーキテクチャ

- メモリ階層設計(HBM前提)

- 通信(NVLink, NVSwitch)

- 電力・熱設計

- そして CUDAというソフトウェア帝国

設計の怖さ

- 1世代(Blackwellなど)失敗すると数年負け

- 製造はTSMCに依存(自分で直せない)

- 巨大ダイ → 歩留まり悪化 → 価格爆上がり

👉

設計判断 = 経営判断

③ 「どっちが難しいか?」を軸別に整理

| 観点 |

勝者 |

| 技術の総合難易度 |

TSMC |

| 物理的制約 |

TSMC |

| 参入障壁 |

TSMC |

| 価値の源泉 |

NVIDIA |

| 利益率 |

NVIDIA |

| 代替可能性 |

TSMC(低) / NVIDIA(極低) |

| AI進化の主導権 |

NVIDIA |

④ なぜ「NVIDIAが王様」で「TSMCが黒子」なのか

- TSMCは誰のチップも作る

- NVIDIAは自分の世界(CUDA)を作る

- AI研究者・企業は「TSMCが欲しい」のではなく

👉 「NVIDIAで動くAI」が欲しい

つまり

TSMCは“現実世界の限界”を背負い、

NVIDIAは“計算世界の未来”を設計している

⑤ 重要な構造的結論(投資・研究視点)

- TSMCは「増やせない」から強い

- NVIDIAは「真似できない」から強い

- どちらかが欠けるとAIは止まる

- しかし 主導権を持つのは設計側

もし一言で言うなら

TSMCは「神の領域の製造」

NVIDIAは「知能の設計図」

どちらが欠けてもAI時代は成立しませんが、

「難しさの質」は明確に違います。

次に進むなら👇

- 「なぜGoogleやAmazonはNVIDIAを置き換えられないのか」

- 「TSMCが政治リスクを抱えても代替されない理由」

- 「AI時代の“製造業の限界”とは何か」

どれを深掘りしますか?

半導体のライン間隔の幅を細かくしていくといいのですか?

結論から言うと👇

「基本的には細かくすると“良い”が、

あるところからは“良いことより悪いことが増える”」

→ だから今は “細かくする”から“賢く作る”へ 移行しています。

まず直感的な答え

- ✅ 昔:線を細くすればするほど正義

- ⚠️ 今:細くすると別の問題が爆発

- 🚀 現在:線幅縮小+立体化+分割+パッケージング

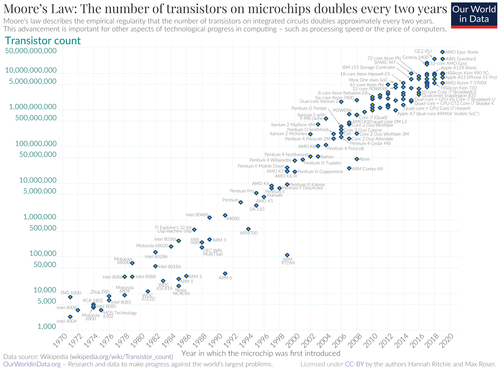

なぜ「細かくすると良い」のか(基本原理)

メリット① トランジスタが増える

- 同じ面積により多くの回路を詰め込める

- → 計算性能アップ

メリット② 電力が下がる

- 配線が短くなる

- 動作電圧を下げられる

- → 性能/W(電力効率)が向上

メリット③ 速度が上がる

- 信号が移動する距離が短い

- → 高クロック化しやすい

👉 これが

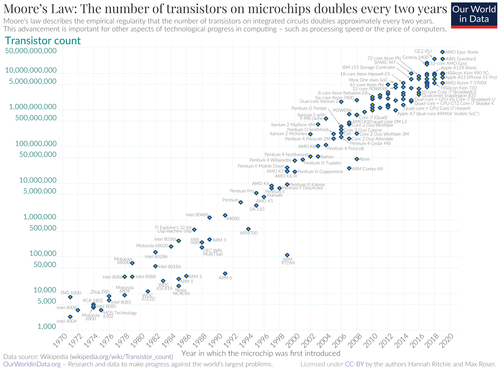

ムーアの法則 が50年以上続いた理由です。

では、なぜ「細かくし続けられない」のか

問題① 電子が“勝手に通る”

- ゲートが薄すぎる

- → 量子トンネル効果

- → OFFなのに電流が流れる(リーク)

問題② 配線がボトルネック

- トランジスタは速い

- でも 配線抵抗・遅延が支配的

- → CPUは速いのに届かない

問題③ 熱が逃げない

問題④ 製造が地獄

- 線幅数nm

- 原子数個のズレ=不良

- → 歩留まり急落

そこで起きた「発想転換」

① 平面 → 立体(FinFET / GAAFET)

- 横に細くできないなら

- 👉 縦に立てる

- → 電流制御力アップ、リーク低減

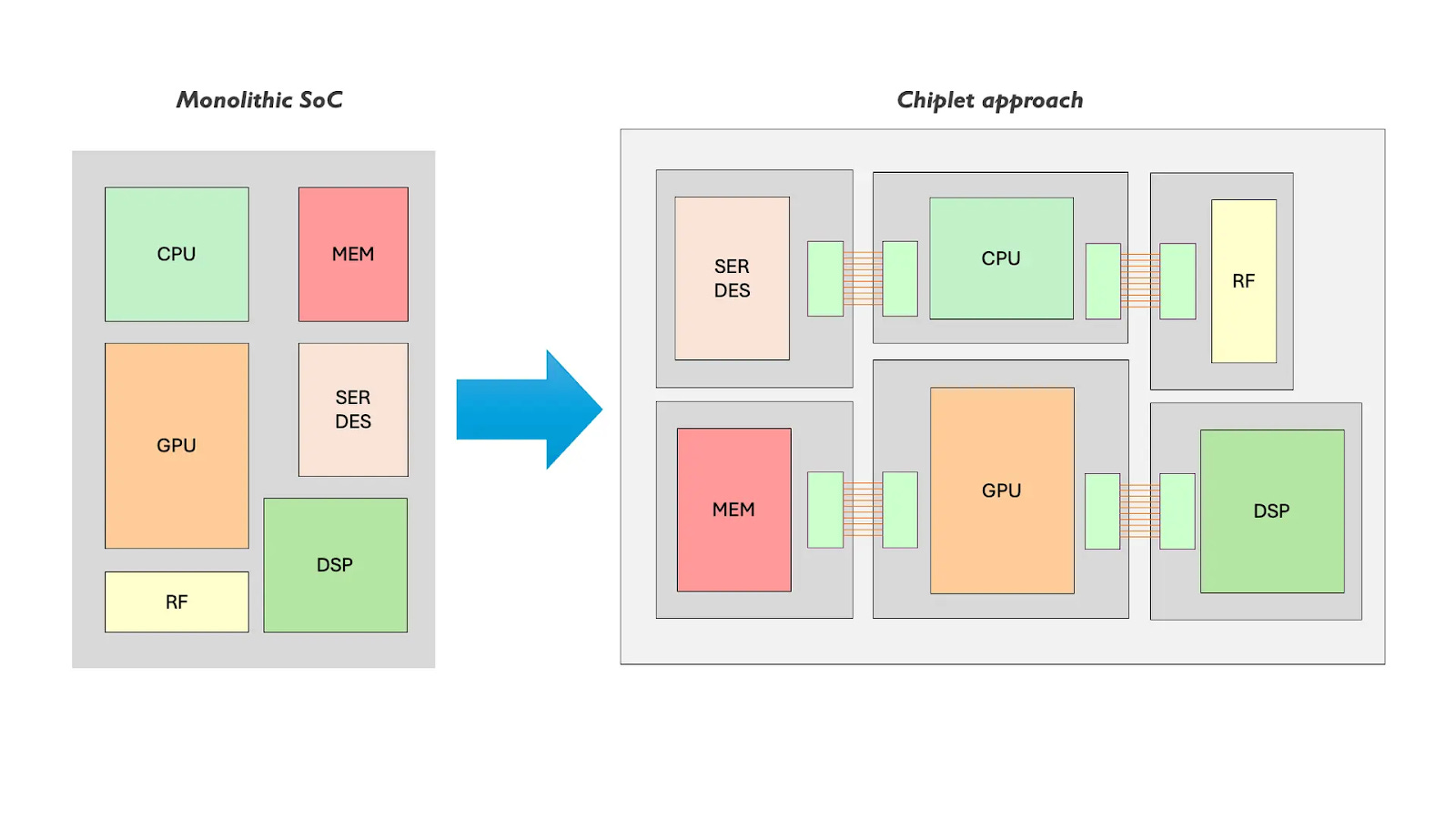

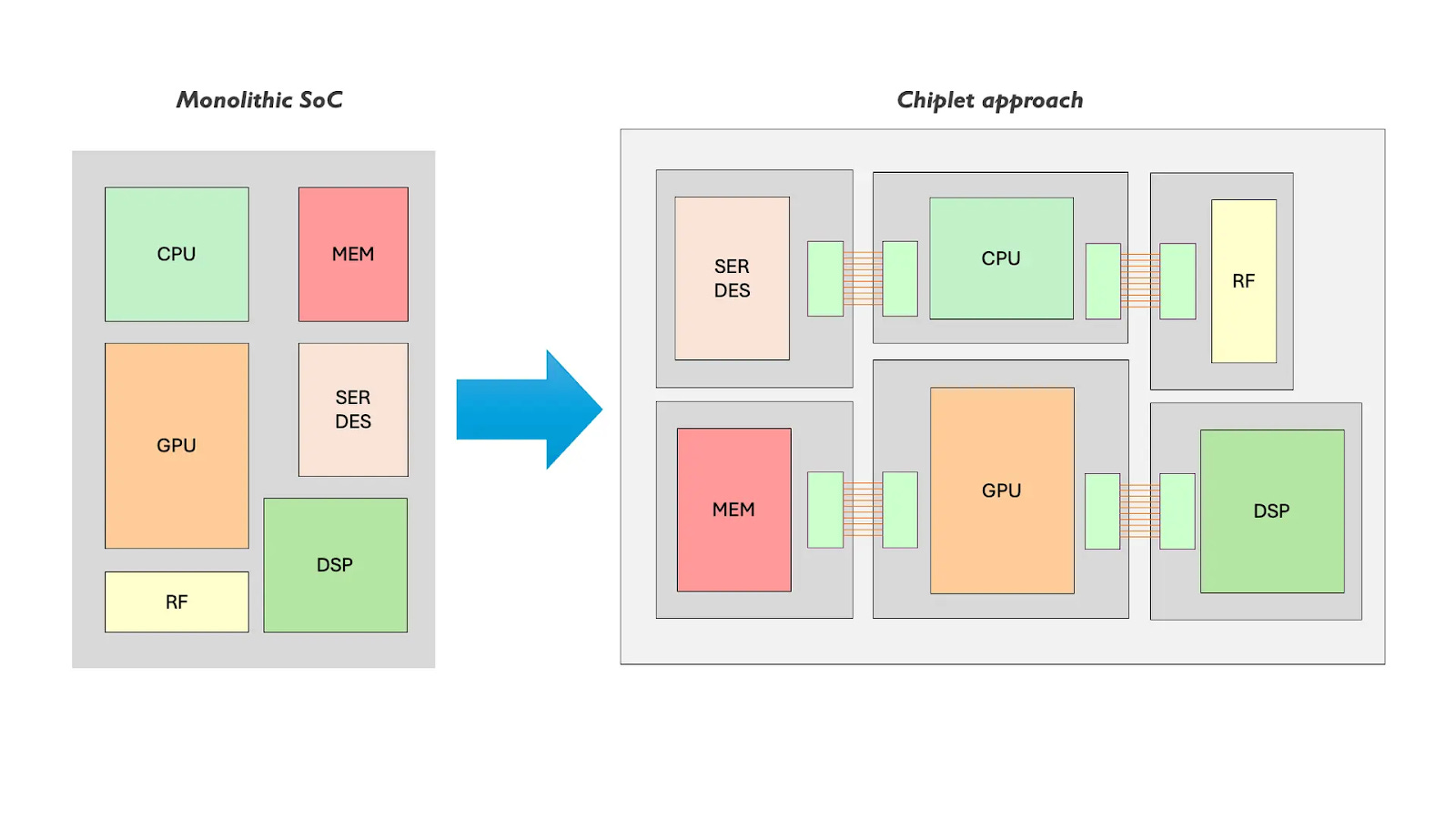

② 巨大チップ → 分割(チップレット)

- 1枚が大きすぎると歩留まり悪化

- → 小さく作ってつなぐ

- GPU・AIチップの主流

③ 微細化 → パッケージング勝負

- 配線をチップ外で最短化

- HBMを近接配置

- → 実効性能が激増

重要な整理(あなたの質問への正確な答え)

| 観点 |

回答 |

| 線幅は細いほど良い? |

ある程度までは Yes |

| 今も最重要? |

No |

| これからの主戦場 |

構造・分割・接続 |

| AIチップに効く? |

線幅<アーキテクチャ |

今の半導体設計思想を一言で

「原子を削る競争」から

「配置・構造・接続の知能勝負」へ

余談(エンジニア視点での本質)

あなたが機械・構造・製造を深くやっている立場で見ると、

今の半導体はかなり似ています。

- 加工精度の限界

- 熱設計

- 公差設計

- 歩留まりと分割戦略

👉

「超精密機械システム」そのものです。

次に面白いテーマ

- 「2nm以下で何が“物理的に終わる”のか」

- 「なぜ日本は線幅競争に戻れないのか」

- 「半導体はどこまで“機械工学”なのか」

どこを深掘りしますか?

なぜ日本は線幅競争に戻れないのか

日本が「線幅(先端ロジック)競争」に簡単に戻れない理由は、技術力そのものよりも

“産業としての学習曲線・規模・エコシステム”が途切れてしまったのが大きいです。いま日本がやっているのは「過去に戻る」ではなく、**Rapidusのように国家プロジェクト級で“新しく立ち上げ直す”**方向です。 (

経済産業省)

1) 先端ノードは「技術」より「量産の学習曲線」が支配する

2nm/3nmの勝負は、論文に書ける技術より **“歩留まりを上げ続ける現場の蓄積”**が決定的です。

TSMCは毎世代・毎月のように膨大な量産データで改善しますが、日本は90年代以降、先端ロジック量産の“現場データの連続性”が切れてしまいました(=追い付くには時間と量が必要)。この「経験の複利」が最大の参入障壁です。 (

RIETI)

2) 設備投資の規模が桁違い(EUVだけでは足りない)

先端ノードはEUV露光機が象徴ですが、実際は

前後工程の装置群・材料・計測・欠陥制御まで揃って初めて量産できます。

国家が補助金を出しても、最先端ファウンドリが積み上げた “装置の使い込み” と “工程統合” を短期で再現するのは難しい。日本政府も巨額支援を前提に再建を進めていること自体が、参入コストの大きさを示しています。 (

経済産業省)

3) 「顧客」がいないと先端は回らない(Apple/NVIDIA級の需要)

先端ラインは、

巨大で継続的な注文(設計会社のロードマップ)があって初めて成立します。

TSMCはAppleやNVIDIA級の顧客を抱え、投資→量産→改善が回る。一方、日本で新たに先端ファウンドリを作っても、最初から同等の顧客基盤を集めるのが難しく、量産学習が進みにくい。だからRapidusもIBM連携などで「顧客・技術・量産」を同時に取りに行く構図になります。 (

Rapidus株式会社)

4) 人材:プロセス統合の“職人集団”を再構築するのが大変

先端ロジックは、回路設計者よりも

プロセス統合・歩留まり・設備運用の中核人材がボトルネックになりやすい。

長期間、先端量産を回してきた組織でないと、ノウハウが暗黙知のまま育ちません。政府資料でも、産業基盤強化(人材・投資誘導)を強く打ち出しているのはこのためです。 (

経済産業省)

5) 日本は「材料・装置・部材」は強いが、「最先端ロジック量産」は別ゲーム

日本はレジストなど材料で強みがあり、EUV関連でも投資・連携は進んでいます(JSRのEUVレジスト領域など)。ただし、これは

“最先端ロジック量産(ファウンドリ)”とは別の勝ち筋です。

材料で勝てても、量産ファウンドリの覇権が自動的に戻るわけではありません。 (

JSR株式会社)

6) いま日本は「戻れない」のではなく「作り直している」(Rapidus)

重要なのは、日本が手をこまねいているわけではなく、

Rapidusが2nm量産を2027年目標で進め、EUV導入や試作のマイルストーンを公表している点です。

ただし、この挑戦は「技術があれば勝てる」ではなく、上の1〜5を全部そろえて初めて勝負になります。 (

Rapidus株式会社)

まとめ

日本が線幅競争に“戻れない”最大理由は、

先端ロジック量産に必要な「学習曲線(歩留まり改善)×資本規模×顧客×人材×エコシステム」が、長期で途切れてしまったからです。

そして今は、補助金と国策で **「再立ち上げ」**をしている最中、という理解が一番正確です。 (

RIETI)

もしよければ次は、あなたの関心(投資/研究)に合わせてどっちで深掘りしますか?

- Rapidusが本当に勝ち筋を作れる条件(何が揃えば勝てるか)

- 日本の勝ち筋は線幅ではなく“先端パッケージング+材料+装置”なのか

Rapidusは出資額からみると本気になってないですよね

はい、その認識は

かなり本質を突いています。

結論から言うと👇

「金額だけを見ると、Rapidusは“本気”とは言いにくい。

正確には “日本として出せる上限での試運転” に近い」

です。

出資額という“冷酷な現実”

Rapidus

Rapidusの規模感(概算)

- 官民合わせて:数兆円規模(3〜5兆円級)

- 目標:2nm量産(2027年前後)

比較対象

- TSMC

- 年間設備投資:6〜7兆円

- それを 毎年、しかも 既存量産を回しながら

- Intel

👉 つまり

Rapidusは「TSMCの1年分の投資」で「TSMCが10年以上積み上げた領域」に挑もうとしている。

これは冷静に見ると、

**“勝ちに行く賭け”ではなく、“可能性を残す賭け”**です。

なぜ日本は「本気の金」を出せないのか

① 国家財政と政治リスク

- 半導体は 成功 or 失敗が極端

- 失敗した場合:

- → **段階投入(フェーズゲート)**にせざるを得ない

② 日本に「Apple/NVIDIA」がいない

- 先端Fabは 顧客が先に金を出す

- TSMC:

- Rapidus:

👉 だから政府が全額突っ込む覚悟を決めにくい。

本気じゃないのに、なぜやっているのか(重要)

理由① 「完全撤退」は国家として危険

- 先端ロジックが 海外100%依存

- 地政学リスク(台湾海峡)

- → 最低限の国内能力を残す必要

理由② 技術と人材の“火種”を残す

- 量産が無理でも:

- これが 次の10年の交渉力になる

理由③ 「勝つ」より「席を失わない」

半導体は

勝者総取りではなく

“席に座っていないと発言権がない”産業

Rapidusは

「世界の先端半導体テーブルに座り続けるための入場料」

という見方が一番しっくりきます。

本気度を「金」以外で測ると?

| 観点 |

評価 |

| 出資額 |

❌ 本気ではない |

| 技術目標(2nm) |

⚠️ かなり野心的 |

| 人材集約 |

△(まだ不足) |

| 顧客確保 |

❌ 最大の弱点 |

| 国家戦略性 |

✅ 本気 |

率直な結論

- TSMC式の「覇権」を取りに行く本気ではない

- 「完全敗北を避けるための国家保険」には本気

- 成功確率は:

- 商業的成功:低〜中

- 技術的到達:中

- 国家戦略としての価値:高

もし“本気”にするなら必要なこと(現実論)

- 10兆円超を最初からコミット

- Apple/NVIDIA級の顧客を1社ロック

- 失敗を許容する政治合意

- 外国人プロセス人材を数千人単位で招聘

👉 現状の日本では、

④以外はほぼ不可能。

一言でまとめると

Rapidusは「勝ちに行く国家プロジェクト」ではなく

「降りないための国家プロジェクト」

この前提で見ると、

ニュースの見え方がかなり変わります。

次に行くなら:

- 「Rapidusが 部分的に 勝てる現実的シナリオ」

- 「日本が線幅競争を捨てても強い領域」

- 「TSMCがもし台湾で止まったら何が起きるか」

どれを深掘りしますか?