過去10年間、機械学習ソフトウェア開発の状況は大きく変化してきました。多くのフレームワークが登場しては消えていったが、そのほとんどはNvidiaのCUDAを活用することに大きく依存し、Nvidia GPUで最高のパフォーマンスを発揮してきた。しかし、PyTorch 2.0やOpenAIのTritonの登場により、この分野でのNvidiaの、主にソフトウェアの堀による支配的な地位は崩れつつある。

本レポートでは、GoogleのTensorFlowがPyTorchに負けた理由、GoogleがAIの初期のリーダーシップを公に活かせなかった理由、機械学習モデルのトレーニング時間の主要な構成要素、メモリ容量/バンド幅/コストの壁、モデルの最適化などのトピックに触れます、 他のAIハードウェア企業がこれまでNvidiaの優位性に食い込めなかった理由、ハードウェアがより重要になり始める理由、CUDAにおけるNvidiaの競争優位性が払拭される方法、Nvidiaの競合他社の1社がトレーニング用シリコン用の大規模クラウドで得た大きな勝利などです。

1,000フィートで要約すると、機械学習モデルのデフォルトのソフトウェアスタックは、もはやNvidiaのクローズドソースであるCUDAではなくなるということです。ボールはNvidiaのコートにあり、彼らはOpenAIとMetaにソフトウェアスタックの主導権を握らせたのです。そのエコシステムは、Nvidiaが独自のツールで失敗したため、独自のツールを構築したのですが、これでNvidiaの堀は永久に弱まることになります。

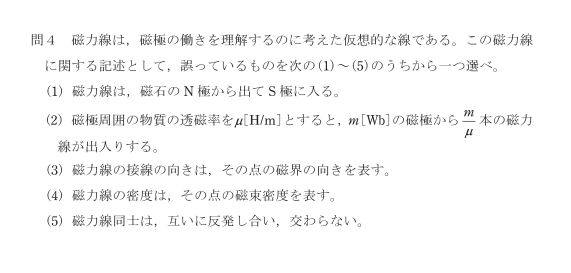

TensorFlow vs. PyTorch

A handful of years ago, the framework ecosystem was quite fragmented, but TensorFlow was the frontrunner. Google looked poised to control the machine learning industry. They had a first movers’ advantage with the most commonly used framework, TensorFlow, and by designing/deploying the only successful AI application-specific accelerator, TPU.

Instead, PyTorch won. Google failed to convert its first mover’s advantage into dominance of the nascent ML industry. Nowadays, Google is somewhat isolated within the machine learning community because of its lack of use of PyTorch and GPUs in favor of its own software stack and hardware. In typical Google fashion, they even have a 2nd framework called Jax that competes directly with TensorFlow.

There’s even endless talk of Google’s dominance in search and natural language processing waning due to large language models, particularly those from OpenAI and the various startups that utilize OpenAI APIs or are building similar foundational models. While we believe this doom and gloom is overblown, that story is for another day. Despite these challenges, Google is still at the forefront of the most advanced machine learning models. They invented transformers and remain state-of-the-art in many areas (PaLM, LaMBDA, Chinchilla, MUM, TPU).

Back to why PyTorch won. While there was an element of wrestling control away from Google, it was primarily due to its increased flexibility and usability of PyTorch versus TensorFlow. If we boil it down to a first principal level, PyTorch differed from TensorFlow in using “Eager mode” rather than "Graph Mode."

Eager mode can be thought of as a standard scripting execution method. The deep learning framework executes each operation immediately, as it is called, line by line, like any other piece of Python code. This makes debugging and understanding your code more accessible, as you can see the results of intermediate operations and see how your model behaves.

In contrast, graph mode has two phases. The first phase is the definition of a computation graph representing the operations to perform. A computation graph is a series of interconnected nodes representing operations or variables, and the edges between nodes represent the data flow between them. The second phase is the deferred execution of an optimized version of the computation graph.

This two-phase approach makes it more challenging to understand and debug your code, as you cannot see what is happening until the end of the graph execution. This is analogous to "interpreted" vs. "compiled" languages, like python vs. C++. It's easier to debug Python, largely since it's interpreted.

While TensorFlow now has Eager mode by default, the research community and most large tech firms have settled around PyTorch. This is exemplified by the fact that nearly ever generative AI model that made the news, being based on PyTorch. The Google generative AI models are based on Jax, not TensorFlow.

Of course there is a long tail of image nets using other frameworks like TensorFlow and Keras, but the compute budgets for new model development is all flowing to PyTorch models. For a deeper explanation of why PyTorch won, see here. In general, if you walk around the halls of NeurIPS (the main AI conference), all generative AI, the non-Google work is with PyTorch.

TensorFlowとPyTorchの比較

数年前、フレームワークのエコシステムはかなり細分化されていましたが、TensorFlowはトップランナーでした。Googleは、機械学習業界を支配する態勢を整えているように見えた。最も一般的に使われているフレームワークであるTensorFlowと、唯一成功したAIアプリケーション専用アクセラレータであるTPUを設計/配備することで、先発者としての優位性を確保していました。

その代わりに、PyTorchが勝利した。Googleは、先行者利益を黎明期のML業界の覇権につなげることができなかったのです。現在、Googleは、PyTorchとGPUを使用せず、独自のソフトウェアスタックとハードウェアを優先しているため、機械学習コミュニティ内でやや孤立しています。Googleの典型的なやり方として、TensorFlowと直接競合するJaxという第2フレームワークまで持っている。

検索や自然言語処理におけるGoogleの優位性は、大規模な言語モデル、特にOpenAIや、OpenAIのAPIを利用したり、同様の基盤モデルを構築しているさまざまな新興企業のモデルによって衰えるという話も後を絶ちません。私たちは、このような悲観的な状況は行き過ぎだと考えていますが、その話はまた別の日にしましょう。このような課題にもかかわらず、Googleは最先端の機械学習モデルの最前線にいます。彼らはトランスフォーマーを発明し、多くの分野で最先端を走り続けています(PaLM、LaMBDA、Chinchilla、MUM、TPU)。

なぜPyTorchが勝ったのかに話を戻す。Googleから主導権を奪い取ったという要素もありますが、主にTensorFlowに対してPyTorchの柔軟性と使い勝手が向上したことが原因です。第一原理レベルにまで煮詰めると、PyTorchはTensorFlowと異なり、"グラフモード "ではなく "イーガーモード "を使っていました。

Eagerモードは、標準的なスクリプトの実行方法と考えることができます。深層学習フレームワークは、各操作が呼び出されると、他のPythonコードと同じように一行ずつ即座に実行する。これにより、中間操作の結果を確認したり、モデルの挙動を確認したりすることができるため、コードのデバッグや理解がより身近になります。

これに対し、グラフモードには2つのフェーズがあります。最初のフェーズは、実行する演算を表す計算グラフを定義することです。計算グラフは、演算や変数を表すノードが相互に接続されたもので、ノード間のエッジはノード間のデータフローを表しています。第2段階は、計算グラフを最適化したものを遅延実行することである。

この2段階のアプローチでは、グラフの実行が終わるまで何が起こっているのかが分からないため、コードの理解やデバッグがより困難になります。これは、パイソンとC++のような「インタプリタ型」言語と「コンパイル型」言語に似ています。Pythonはインタプリタ言語であるため、デバッグが容易なのです。

TensorFlowはデフォルトでEagerモードを備えていますが、研究コミュニティやほとんどの大手技術会社はPyTorchに落ち着いています。これは、ニュースになったほぼすべての生成AIモデルが、PyTorchをベースにしているという事実に象徴されています。Googleの生成AIモデルは、TensorFlowではなくJaxをベースにしています。

もちろん、TensorFlowやKerasといった他のフレームワークを使ったイメージネットのロングテールもありますが、新しいモデル開発のための計算予算はすべてPyTorchのモデルに流れています。なぜPyTorchが勝利したのか、より深い説明はこちらをご覧ください。一般的に、NeurIPS(メインのAIカンファレンス)の会場を歩くと、生成AI、Google以外の仕事はすべてPyTorchを使っています。

Machine Learning Training Components

If we boil machine learning model training to its most simplistic form, there are two major time components in a machine learning model’s training time.

Compute (FLOPS): Running dense matrix multiplication within each layer

Memory (Bandwidth): Waiting for data or layer weights to get to the compute resources. Common examples of bandwidth-constrained operations are various normalizations, pointwise operations, SoftMax, and ReLU.

In the past, the dominant factor in machine learning training time was compute time, waiting for matrix multiplies. As Nvidia’s GPUs continued to develop, this quickly faded away from being the primary concern.

Nvidia’s FLOPS have increased multiple orders of magnitude by leveraging Moore’s Law, but primarily architectural changes such as the tensor core and lower precision floating point formats. In contrast, memory has not followed the same path.

If we go back to 2018, when the BERT model was state of the art, and the Nvidia V100 was the most advanced GPU, we could see that matrix multiplication was no longer the primary factor for improving a model’s performance. Since then, the most advanced models have grown 3 to 4 orders of magnitude in parameter count, and the fastest GPUs have grown an order of magnitude in FLOPS.

Even in 2018, purely compute-bound workloads made up 99.8% of FLOPS but only 61% of the runtime. The normalization and pointwise ops achieve 250x less FLOPS and 700x less FLOPS than matrix multiplications, respectively, yet they consume nearly 40% of the model’s runtime.

機械学習トレーニングの構成要素

機械学習モデルの学習を最も単純化した形で煮詰めると、機械学習モデルの学習時間には大きく分けて2つの時間要素がある。

計算(FLOPS): 各層で密な行列の乗算を実行する

メモリ(Bandwidth): メモリ(帯域幅):データやレイヤーの重みが計算リソースに到達するのを待つ。帯域幅に制約のある演算の一般的な例として、さまざまな正規化、ポイントワイズ演算、SoftMax、ReLUがあります。

以前は、機械学習のトレーニング時間における主要な要因は、行列の乗算を待つ計算時間でした。NvidiaのGPUが発展し続けるにつれて、これはすぐに主要な関心事から消え去りました。

NvidiaのFLOPSは、ムーアの法則を活用しながら、主にテンソルコアや低精度浮動小数点フォーマットなどのアーキテクチャの変更によって、複数桁の増加を遂げました。これに対して、メモリは同じ道をたどっていない。

BERTモデルが最先端であり、Nvidia V100が最先端のGPUであった2018年まで遡ると、行列の乗算がモデルの性能を向上させる主要因ではなくなっていることがわかります。それ以来、最先端のモデルはパラメータ数で3~4桁、最速のGPUはFLOPSで1桁の成長を遂げています。

2018年においても、純粋な計算負荷はFLOPSの99.8%を占めるが、ランタイムの61%に過ぎない。正規化とポイントワイズオペは、行列の乗算に比べてそれぞれ250倍少ないFLOPSと700倍少ないFLOPSを実現していますが、モデルのランタイムの40%近くを消費しています。

The Memory Wall

As models continue to soar in size, large language models take 100s gigabytes, if not terabytes, for the model weights alone. Production recommendation networks deployed by Baidu and Meta require dozens of terabytes of memory for their massive embedding tables. A huge chunk of the time in large model training/inference is not spent computing matrix multiplies, but rather waiting for data to get to the compute resources. The obvious question is why don’t architects put more memory closer to the compute. The answer is $$$.

Memory follows a hierarchy from close and fast to slow and cheap. The nearest shared memory pool is on the same chip and is generally made of SRAM. Some machine-learning ASICs attempt to utilize huge pools of SRAM to hold model weights, but there are issues with this approach. Even Cerebras’ ~$2,500,000 wafer scale chips only have 40GB of SRAM on the chip. There isn’t enough memory capacity to hold the weights of a 100B+ parameter model.

Nvidia’s architecture has always used a much smaller amount of memory on the die. The current generation A100 has 40MB, and the next generation H100 has 50MB. 1GB of SRAM on TSMC’s 5nm process node would require ~200mm^2 of silicon. Once the associated control logic/fabric are implemented, that would require over 400mm^2 of silicon, or about 50% of the total logic area of an Nvidia datacenter GPU. Given that an A100 GPU costs $10k+ and the H100 is more like $20k+, economically, this is infeasible. Even when you ignore Nvidia’s ~75% gross margin on datacenter GPUs (~4x markup), the cost per GB of SRAM memory would still be in the $100s for a fully yielded product.

Furthermore, the cost of on-chip SRAM memory will not decrease much through conventional Moore’s Law process technology shrinks. The same 1GB of memory actually costs more with the next-generation TSMC 3nm process technology. While 3D SRAM will help with SRAM costs to some degree, that is only a temporary bend of the curve.

The next step down in the memory hierarchy is tightly coupled off-chip memory, DRAM. DRAM has an order magnitude higher latency than SRAM (~>100 nanoseconds vs. ~10 nanoseconds), but it’s also much cheaper ($1s a GB vs. $100s GB.)

DRAM followed the path of Moore’s Law for many decades. When Gordon Moore coined the term, Intel’s primary business was DRAM. His economic prediction about density and cost of transistors generally held true until ~2009 for DRAM. Since ~2012 though, the cost of DRAM has barely improved.

The demands for memory have only increased. DRAM now comprises 50% of the total server’s cost. This is the memory wall, and it has shown up in products. Comparing Nvidia’s 2016 P100 GPU to their 2022 H100 GPU that is just starting to ship, there is a 5x increase in memory capacity (16GB -> 80GB) but a 46x increase in FP16 performance (21.2 TFLOPS -> 989.5 TFLOPS).

While capacity is a significant bottleneck, it is intimately tied to the other major bottleneck, bandwidth. Increased memory bandwidth is generally obtained through parallelism. While standard DRAM is only a few dollars per GB today, to get the massive bandwidth machine learning requires, Nvidia uses HBM memory, a device comprised of 3D stacked layers of DRAM that requires more expensive packaging. HBM is in the $10 to $20 a GB range, including packaging and yield costs.

The cost constraints of memory bandwidth and capacity show up in Nvidia’s A100 GPUs constantly. The A100 tends to have very low FLOPS utilization without heavy optimization. FLOPS utilization measures the total computed FLOPS required to train a model vs. the theoretical FLOPS the GPUs could compute in a model’s training time.

Even with heavy optimizations from leading researchers, 60% FLOPS utilization is considered a very high utilization rate for large language model training. The rest of the time is overhead, idle time spent waiting for data from another calculation/memory, or recomputing results just in time to reduce memory bottlenecks.

From the current generation A100 to the next generation H100, the FLOPS grow by more than 6X, but memory bandwidth only grows by 1.65x. This has led to many fears of low utilization for H100. The A100 required many tricks to get around the memory wall, and more will need to be implemented with the H100.

The H100 brings distributed shared memory and L2 multicast to Hopper. The idea is that different SMs (think cores) can write directly to another SM’s SRAM (shared memory/L1 Cache). This effectively increases the size of the cache and reduces the required bandwidth of DRAM read/writes. Future architectures will rely on sending fewer operations to memory to minimize the impact of the memory wall. It should be noted that larger models tend to achieve higher utilization rates as FLOPS demands scale more exponentially whereas memory bandwidth and capacity demands tend to scale more linearly.

メモリの壁

モデルのサイズが大きくなるにつれて、大規模な言語モデルは、モデルの重みだけで100ギガバイト、いやテラバイトを必要とします。BaiduやMetaが展開するプロダクション・レコメンデーション・ネットワークは、巨大な埋め込みテーブルのために数十テラバイトのメモリを必要とします。大規模なモデルのトレーニングや推論にかかる時間の大部分は、行列の掛け算の計算ではなく、データが計算リソースに届くのを待つことに費やされています。なぜアーキテクトはより多くのメモリをコンピュートリソースに近づけることができないのだろうか?その答えは、$$$です。

メモリは、近くて速いものから遅くて安いものまで、階層的に配置されています。最も近い共有メモリプールは、同じチップ上にあり、一般にSRAMでできています。機械学習ASICの中には、モデルの重みを保持するためにSRAMの巨大なプールを利用しようとするものがありますが、このアプローチには問題があります。セレブラの約250万円のウェハースケールチップでさえ、チップ上に40GBのSRAMしか搭載していません。100B以上のパラメータモデルの重みを保持するには、十分なメモリ容量がないのです。

Nvidiaのアーキテクチャは、常にダイ上でより少ない量のメモリを使用してきました。現世代のA100は40MB、次世代H100は50MBです。TSMCの5nmプロセスノードで1GBのSRAMを搭載すると、~200mm^2のシリコンを必要とします。関連する制御ロジックやファブリックが実装されると、400mm^2以上のシリコンが必要になり、Nvidiaのデータセンター向けGPUの総ロジック面積の約50%に相当します。A100GPUが1万ドル以上、H100が2万ドル以上することを考えると、経済的にこれは実現不可能です。Nvidiaのデータセンター向けGPUの粗利益率(~4倍)を無視しても、SRAMメモリの1GBあたりのコストは、完全に生産された製品で100ドル台となります。

さらに、オンチップSRAMメモリのコストは、従来のムーアの法則に基づくプロセス技術の縮小によっても、それほど低下することはありません。同じ1GBのメモリでも、次世代のTSMC 3nmプロセス技術では、実際にはもっとコストがかかる。3D SRAMはSRAMのコストにある程度貢献するだろうが、それは一時的にカーブを曲げたに過ぎない。

メモリ階層の次のステップは、密結合のオフチップメモリであるDRAMです。DRAMはSRAMに比べてレイテンシが桁違いに高い(~100ナノ秒、~10ナノ秒)ですが、価格もはるかに安いです(1GBあたり1ドル、100GBあたり1ドルです)。

DRAMは、何十年もの間、ムーアの法則の道を歩んできました。ゴードン・ムーアがこの言葉を作ったとき、インテルの主要事業はDRAMでした。トランジスタの集積度とコストに関するムーアの経済予測は、DRAMについては2009年まで概ね正しかった。しかし、2012年以降、DRAMのコストはほとんど向上していません。

しかし、メモリに対する要求は高まるばかりです。現在、DRAMはサーバーの総コストの50%を占めています。これがメモリの壁であり、製品にも表れている。Nvidiaの2016年のP100 GPUと、出荷が始まったばかりの2022年のH100 GPUを比較すると、メモリ容量は5倍(16GB→80GB)だが、FP16性能は46倍(21.2 TFLOPS→989.5 TFLOPS)である。

容量は重要なボトルネックですが、もう一つの大きなボトルネックである帯域幅と密接に結びついています。メモリ帯域幅の拡大は、一般に並列化によって得られる。標準的な DRAM の価格は 1GB あたり数ドルですが、機械学習が必要とする膨大な帯域幅を得るために、Nvidia 社は HBM メモリを使用しています。このデバイスは、DRAM の 3D スタック層で構成されており、より高価なパッケージが必要です。HBMは、パッケージングと歩留まりコストを含めて、1GBあたり10ドルから20ドルの範囲にある。

メモリの帯域幅と容量というコストの制約は、NvidiaのA100 GPUに常に現れています。A100は、高度な最適化を行わないと、FLOPS利用率が非常に低くなる傾向がある。FLOPS利用率は、モデルのトレーニングに必要な総計算FLOPSと、GPUがモデルのトレーニング時間内に計算できる理論FLOPSを比較したものです。

第一線の研究者が高度な最適化を行ったとしても、大規模言語モデルの学習において60%のFLOPS利用率は非常に高い利用率であると考えられています。残りの時間はオーバーヘッド、別の計算/メモリからのデータを待つために費やされるアイドル時間、またはメモリのボトルネックを減らすためにギリギリで結果を再計算している時間である。

現世代のA100から次世代のH100まで、FLOPSは6倍以上成長するが、メモリ帯域は1.65倍しか成長しない。そのため、H100の低稼働を危惧する声が多く聞かれるようになりました。A100ではメモリの壁を回避するために多くのトリックが必要でしたが、H100ではさらに多くのトリックを実装する必要があります。

H100は、分散共有メモリとL2マルチキャストをHopperにもたらす。このアイデアは、異なるSM(コアと呼ぶ)が別のSMのSRAM(共有メモリ/L1キャッシュ)に直接書き込むことができるというものです。これにより、キャッシュのサイズが効果的に増加し、DRAMの読み書きに必要な帯域幅が削減されます。将来のアーキテクチャでは、メモリウォールによる影響を最小化するために、より少ないオペレーションをメモリに送ることに頼ることになるでしょう。FLOPSの需要が指数関数的に拡大するのに対し、メモリの帯域幅と容量の需要は線形に拡大する傾向があるため、大型のモデルほど高い利用率を達成できる傾向にあることに留意する必要があります。

Operator Fusion – The Workaround

Just like with training ML models, knowing what regime you're in allows you to narrow in on optimizations that matters. For example, if you're spending all of your time doing memory transfers (i.e. you are in a memory-bandwidth bound regime), then increasing the FLOPS of your GPU won't help. On the other hand, if you're spending all of your time performing big chonky matmuls (i.e. a compute-bound regime), then rewriting your model logic into C++ to reduce overhead won't help.

https://horace.io/brrr_intro.html

Referring back to why PyTorch won, it was the increased flexibility and usability due to Eager mode, but moving to Eager mode isn’t all sunshine and rainbows. When executing in Eager mode, each operation is read from memory, computed, then sent to memory before the next operation is handled. This significantly increases the memory bandwidth demands if heavy optimizations aren’t done.

As such, one of the principal optimization methods for a model executed in Eager mode is called operator fusion. Instead of writing each intermediate result to memory, operations are fused, so multiple functions are computed in one pass to minimize memory reads/writes. Operator fusion improves operator dispatch, memory bandwidth, and memory size costs.

This optimization often involves writing custom CUDA kernels, but that is much more difficult than using simple python scripts. As a built-in compromise, PyTorch steadily implemented more and more operators over time natively within PyTorch. Many of these operators were simply multiple commonly used operations fused into a single, more complex function.

The increase in operators made both creating the model within PyTorch easier and the performance of Eager mode faster due to having fewer memory read/writes. The downside was that PyTorch ballooned to over 2,000 operators over a few years.

We would say software developers are lazy, but let’s be honest, almost all people are lazy. If they get used to one of the new operators within PyTorch, they will continue to use that. The developer may not even recognize the performance improvement but instead, use that operator because it means writing less code.

Additionally, not all operations can be fused. A significant amount of time is often spent deciding which operations to fuse and which operations to assign to specific compute resources at the chip and cluster levels. The strategy of which operations to fuse where, although generally similar, does vary significantly depending on the architecture.

Nvidia Is King

The growth in operators and position as the default has helped Nvidia as each operator was quickly optimized for their architecture but not for any other hardware. If an AI hardware startup wanted to fully implement PyTorch, that meant supporting the growing list of 2,000 operators natively with high performance.

The talent level required to train a massive model with high FLOPS utilization on a GPU grows increasingly higher because of all the tricks needed to extract maximum performance. Eager mode execution plus operator fusion means that software, techniques, and models that are developed are pushed to fit within the ratios of compute and memory that the current generation GPU has.

Everyone developing machine learning chips is beholden to the same memory wall. ASICs are beholden to supporting the most commonly used frameworks. ASICs are beholden to the default development methodology, GPU-optimized PyTorch code with a mix of Nvidia and external libraries. An architecture that eschews a GPU’s various non-compute baggage in favor of more FLOPS and a stiffer programming model makes very little sense in this context.

Ease of use is king.

The only way to break the vicious cycle is for the software that runs models on Nvidia GPUs to transfer seamlessly to other hardware with as little effort as possible. As model architectures stabilize and abstractions from PyTorch 2.0, OpenAI Triton, and MLOps firms such as MosaicML become the default, the architecture and economics of the chip solution starts to become the biggest driver of the purchase rather than the ease of use afforded to it by Nvidia’s superior software.

オペレーターフュージョン - 回避策

MLモデルのトレーニングの場合と同様に、どのような領域にいるのかを知ることで、重要な最適化を絞り込むことができます。たとえば、すべての時間をメモリ転送に費やしている場合(つまり、メモリ帯域幅に制約のある領域)、GPUのFLOPSを増やしても効果はありません。一方、大きな計算をすることに時間を費やしている場合(つまり、計算に縛られる領域)、オーバーヘッドを減らすためにモデルロジックをC++に書き換えても、役に立ちません。

https://horace.io/brrr_intro.html

PyTorchが勝った理由は、Eagerモードによる柔軟性と使い勝手の向上でしたが、Eagerモードへの移行は太陽と虹のようなものばかりではありません。Eagerモードで実行する場合、各操作はメモリから読み込まれ、計算された後、次の操作が処理される前にメモリに送られます。このため、高度な最適化を行わないと、メモリ帯域の要求が大幅に増加する。

そのため、Eagerモードで実行されるモデルの主要な最適化手法の1つに、演算子融合というものがあります。各中間結果をメモリに書き込む代わりに、演算を融合させ、複数の関数を1回の処理で計算し、メモリの読み書きを最小限に抑えます。演算子融合により、演算子の派遣、メモリ帯域幅、メモリサイズのコストが改善されます。

この最適化には、カスタムCUDAカーネルを書くことがよくありますが、それは単純なPythonスクリプトを使うよりもはるかに困難です。組み込みの妥協案として、PyTorchは時間の経過とともに、より多くの演算子をPyTorch内にネイティブに着実に実装していきました。これらの演算子の多くは、よく使われる複数の演算を、より複雑な1つの関数に融合させただけのものでした。

演算子の増加により、PyTorch内でのモデルの作成が容易になり、メモリの読み書きが少なくなるため、Eagerモードのパフォーマンスが速くなりました。しかし、その反面、PyTorchは数年で2,000を超える演算子に膨れ上がってしまいました。

ソフトウェア開発者は怠け者だと言いたいところですが、正直に言うと、ほとんどすべての人が怠け者です。PyTorchの中の新しい演算子の1つに慣れてしまうと、その演算子を使い続けてしまうのです。開発者は性能の向上を認識せずに、より少ないコードを書くことになるのでその演算子を使うかもしれません。

さらに、すべての演算を融合できるわけではありません。チップやクラスタレベルで、どの演算を融合させ、どの演算を特定の計算リソースに割り当てるかを決めるのに、かなりの時間を費やすことが多い。どの演算をどこに融合させるかという戦略は、一般的に似ているとはいえ、アーキテクチャによって大きく異なります。

Nvidiaは王者である

各オペレータは、自社のアーキテクチャにはすぐに最適化されるが、他のハードウェアには最適化されないため、オペレータの増加とデフォルトとしての地位は、Nvidiaを助けている。AIハードウェアのスタートアップがPyTorchを完全に実装しようと思えば、増え続ける2,000のオペレータを高いパフォーマンスでネイティブにサポートすることを意味します。

GPU上で高いFLOPS利用率で大規模なモデルを訓練するために必要な人材レベルは、最大限のパフォーマンスを引き出すために必要なあらゆるトリックのために、ますます高くなります。イーガーモード実行+演算子融合は、開発するソフトウェア、技術、モデルが、現世代GPUが持つコンピュートとメモリの比率の中に収まるように押し込まれることを意味します。

機械学習チップを開発する誰もが、同じメモリの壁に屈している。ASICは、最も一般的に使用されているフレームワークをサポートすることに固執しています。ASICは、デフォルトの開発手法である、Nvidiaと外部ライブラリの混合によるGPU最適化PyTorchコードに従順です。より多くのFLOPSとより厳しいプログラミング・モデルを求めて、GPUのさまざまな非競技的な荷物を避けるアーキテクチャは、この文脈ではほとんど意味をなさない。

使い勝手の良さは王道です。

悪循環を断ち切る唯一の方法は、Nvidia GPU上でモデルを実行するソフトウェアが、できるだけ少ない労力で他のハードウェアにシームレスに移行できるようにすることです。モデルのアーキテクチャが安定し、PyTorch 2.0、OpenAI Triton、MosaicMLなどのMLOps企業の抽象化がデフォルトになると、チップソリューションのアーキテクチャと経済性が、Nvidiaの優れたソフトウェアによって与えられる使いやすさよりも、購入の最大の要因になり始めるのである。

PyTorch 2.0

The PyTorch Foundation was established and moved out from under the wings of Meta just a few months ago. Alongside this change to an open development and governance model, 2.0 has been released for early testing with full availability in March. PyTorch 2.0 brings many changes, but the primary difference is that it adds a compiled solution that supports a graph execution model. This shift will make properly utilizing various hardware resources much easier.

PyTorch 2.0 brings an 86% performance improvement for training on Nvidia’s A100 and 26% on CPUs for inference! This dramatically reduces the compute time and cost required for training a model. These benefits could extend to other GPUs and accelerators from AMD, Intel, Tenstorrent, Luminous Computing, Tesla, Google, Amazon, Microsoft, Marvell, Meta, Graphcore, Cerebras, SambaNova, etc.

The performance improvements from PyTorch 2.0 will be larger for currently unoptimized hardware. Meta and other firms’ heavy contribution to PyTorch stems from the fact that they want to make it easier to achieve higher FLOPS utilization with less effort on their multi-billion-dollar training clusters made of GPUs. They are also motivated to make their software stacks more portable to other hardware to introduce competition to the machine learning space.

PyTorch 2.0 also brings advancements to distributed training with better API support for data parallelism, sharding, pipeline parallelism, and tensor parallelism. In addition, it supports dynamic shapes natively through the entire stack, which among many other examples, makes varying sequence lengths for LLMs much easier to support. This is the first time a major compiler supports Dynamic Shapes from training to inference.

PrimTorch

Writing a performant backend for PyTorch that fully supports all 2,000+ operators has been difficult for every machine learning ASIC except for Nvidia GPUs. PrimTorch brings the number of operators down to ~250 primitive operators while also keeping usability unchanged for end users of PyTorch. PrimTorch makes the implementation of different, non-Nvidia backends to PyTorch much simpler and more accessible. Custom hardware and system vendors can bring up their software stacks more easily.

TorchDynamo

Moving to graph mode requires a robust graph definition. Meta and PyTorch have been attempting to work on implementing this for ~5 years, but every solution they came up with had significant drawbacks. They finally cracked the puzzle with TorchDynamo. TorchDynamo will ingest any PyTorch user script, including those that call outside 3rd party libraries, and generate an FX graph.

Dynamo lowers all complex operations to the ~250 primitive operations in PrimTorch. Once the graph is formed, unused operations are discarded, and the graph determines which intermediate operations need to be stored or written to memory and which can potentially be fused. This dramatically reduces the overhead within a model while also being seamless for the user.

TorchDynamo already works for over 99% of the 7,000 PyTorch models tested, including those from OpenAI, HuggingFace, Meta, Nvidia, Stability.AI, and more, without any changes to the original code. The 7,000 models tested were indiscriminately chosen from the most popular projects using PyTorch on GitHub.

Google’s TensorFlow/Jax and other graph mode execution pipelines generally require the user to ensure their model fits into the compiler architecture so that the graph can be captured. Dynamo changes this by enabling partial graph capture, guarded graph capture, and just-in-time recapture.

Partial graph capture allows the model to include unsupported/non-python constructs. When a graph cannot be generated for that portion of the model, a graph break is inserted, and the unsupported constructs will be executed in eager mode between the partial graphs.

Guarded graph capture checks if the captured graph is valid for execution. A guard is a change that would require recompilation. This is important because running the same code multiple times won't recompile multiple times.

Just-in-time recapture allows the graph to be recaptured if the captured graph is invalid for execution.

PyTorch’s goal is to create a unified front end with a smooth UX that leverages Dynamo to generate graphs. The user experience of this solution would be unchanged, but the performance can be significantly improved. Capturing the graph means execution can be parallelized more efficiently over a large base of compute resources.

Dynamo and AOT Autograd then pass the optimized FX graphs to the PyTorch native compiler level, TorchInductor. Hardware companies can also take this graph and input it into their own backend compilers.

PyTorch 2.0

数ヶ月前にPyTorch Foundationが設立され、Metaの翼の下を離れました。このオープンな開発とガバナンスモデルへの変更と同時に、2.0が早期テストのためにリリースされ、3月に完全な利用が可能になりました。PyTorch 2.0は多くの変更をもたらしますが、主な違いは、グラフ実行モデルをサポートするコンパイルされたソリューションが追加されたことです。このシフトにより、様々なハードウェアリソースを適切に利用することがより容易になります。

PyTorch 2.0は、NvidiaのA100でのトレーニングで86%、推論ではCPUで26%の性能向上をもたらしています!これにより、モデルのトレーニングに必要な計算時間とコストを劇的に削減することができます。これらの利点は、AMD、Intel、Tenstorrent、Luminous Computing、Tesla、Google、Amazon、Microsoft、Marvell、Meta、Graphcore、Cerebras、SambaNovaなどの他のGPUやアクセラレータにも適用可能です。

PyTorch 2.0による性能向上は、現在最適化されていないハードウェアではより大きくなります。Meta社やその他の企業がPyTorchに大きく貢献しているのは、GPUで構成された数十億ドル規模のトレーニングクラスタにおいて、より少ない労力でより高いFLOPS利用率を達成することを容易にしたいからであります。また、機械学習分野に競争をもたらすために、自社のソフトウェアスタックを他のハードウェアにもっと移植できるようにしたいという動機もあるようです。

PyTorch 2.0では、データ並列、シャーディング、パイプライン並列、テンソル並列のAPIサポートが強化され、分散学習にも進化を遂げています。さらに、スタック全体を通してネイティブに動的な形状をサポートすることで、LLMのシーケンス長を変化させることがより簡単になりました。主要なコンパイラが学習から推論までダイナミックシェイプをサポートするのは、これが初めてです。

プリムトーチ

2,000以上の演算子を完全にサポートするPyTorch用の高性能なバックエンドを書くことは、Nvidia GPUを除くすべての機械学習ASICにとって難しいことでした。PrimTorchは、PyTorchのエンドユーザーにとって使い勝手が変わらないようにしながら、演算子の数を〜250個のプリミティブ演算子まで減らしています。PrimTorchは、PyTorchへの異なる非Nvidiaのバックエンドの実装をよりシンプルでアクセスしやすいものにします。カスタムハードウェアやシステムベンダーは、より簡単にソフトウェアスタックを導入することができます。

TorchDynamo

グラフモードへの移行には、堅牢なグラフ定義が必要です。MetaとPyTorchは5年前からこの実装を試みてきましたが、どのソリューションも大きな欠点がありました。そして、ついにTorchDynamoでその謎を解き明かした。TorchDynamoは、外部のサードパーティライブラリを呼び出すものも含めて、あらゆるPyTorchユーザスクリプトを取り込み、FXグラフを生成します。

Dynamoは、複雑な演算をPrimTorchの250程度のプリミティブな演算に落とし込みます。グラフが形成されると、未使用の操作は破棄され、グラフは、メモリに保存または書き込む必要がある中間操作と、融合できる可能性のある中間操作を決定する。これにより、モデル内のオーバーヘッドが劇的に削減されるとともに、ユーザーにとってもシームレスなものとなります。

TorchDynamoは、OpenAI、HuggingFace、Meta、Nvidia、Stability.AIなどのモデルを含む、テストした7000のPyTorchモデルの99%以上で、元のコードに変更を加えずに既に動作します。テストした7,000のモデルは、GitHubでPyTorchを使用している最も人気のあるプロジェクトから無差別に選ばれたものです。

GoogleのTensorFlow/Jaxやその他のグラフモード実行パイプラインでは、一般的に、グラフをキャプチャできるように、ユーザーが自分のモデルがコンパイラのアーキテクチャに適合していることを確認する必要があります。Dynamoは、部分的なグラフキャプチャ、ガードされたグラフキャプチャ、およびジャストインタイム再キャプチャを可能にすることでこれを変更します。

部分的なグラフのキャプチャは、モデルがサポートされていない/非Pythonの構成要素を含むことを可能にします。モデルのその部分に対してグラフを生成できない場合、グラフの区切りが挿入され、サポートされていない構成要素は部分グラフの間でイーガーモードで実行されます。

ガード付きグラフキャプチャは、キャプチャされたグラフが実行に有効かどうかをチェックする。ガードとは、再コンパイルが必要になるような変更のことです。同じコードを複数回実行しても、複数回再コンパイルされることはないので、これは重要です。

ジャストインタイム再キャプチャは、キャプチャしたグラフが実行に無効な場合、グラフを再キャプチャすることができます。

PyTorchの目標は、Dynamoを活用してグラフを生成する、スムーズなUXを備えた統一フロントエンドを作ることです。このソリューションのユーザーエクスペリエンスは変わりませんが、パフォーマンスを大幅に向上させることができます。グラフをキャプチャすることで、大規模な計算リソース上でより効率的に実行を並列化することができるのです。

DynamoとAOT Autogradは、最適化されたFXグラフをPyTorchのネイティブコンパイラレベルであるTorchInductorに渡します。ハードウェアメーカーもこのグラフを受け取り、自社のバックエンドコンパイラに入力することができます。

TorchInductor

TorchInductor is a python native deep learning compiler that generates fast code for multiple accelerators and backends. Inductor will take the FX graphs, which have ~250 operators, and lowers them to ~50 operators. Inductor then moves to a scheduling phase where operators are fused, and memory planning is determined.

Inductor then goes to the “Wrapper Codegen,” which generates code that runs on the CPU, GPU, or other AI accelerators. The wrapper codegen replaces the interpreter part of a compiler stack and can call kernels and allocate memory. The backend code generation portion leverages OpenAI Triton for GPUs and outputs PTX code. For CPUs, an Intel compiler generates C++ (will work on non-Intel CPUs too).

More hardware will be supported going forward, but the key is that Inductor dramatically reduces the amount of work a compiler team must do when making a compiler for their AI hardware accelerator. Furthermore, the code is more optimized for performance. There are significant reductions in memory bandwidth and capacity requirements.

We didn't want to build a compiler that only supported GPUs. We wanted something that could scale to support a wide variety of hardware back ends, and having a C++ as well as [OpenAI] Triton forces that generality.

Jason Ansel – Meta AI

OpenAI Triton

OpenAI’s Triton is very disruptive angle to Nvidia’s closed-source software moat for machine learning. Triton takes in Python directly or feeds through the PyTorch Inductor stack. The latter will be the most common use case. Triton then converts the input to an LLVM intermediate representation and then generates code. In the case of Nvidia GPUs, it directly generates PTX code, skipping Nvidia’s closed-source CUDA libraries, such as cuBLAS, in favor of open-source libraries, such as cutlass.

CUDA is commonly used by those specializing in accelerated computing, but it is less well-known among machine learning researchers and data scientists. It can be challenging to use efficiently and requires a deep understanding of the hardware architecture, which can slow down the development process. As a result, machine learning experts may rely on CUDA experts to modify, optimize, and parallelize their code.

Triton bridges the gap enabling higher-level languages to achieve performance comparable to those using lower-level languages. The Triton kernels themselves are quite legible to the typical ML researcher which is huge for usability. Triton automates memory coalescing, shared memory management, and scheduling within SMs. Triton is not particularly helpful for the element-wise matrix multiplies, which are already done very efficiently. Triton is incredibly useful for costly pointwise operations and reducing overhead from more complex operations such as Flash Attention that involve matrix multiplies as a portion of a larger fused operation.

OpenAI Triton only officially supports Nvidia GPUs today, but that is changing in the near future. Multiple other hardware vendors will be supported in the future, and this open-source project is gaining incredible steam. The ability for other hardware accelerators to integrate directly into the LLVM IR that is part of Triton dramatically reduces the time to build an AI compiler stack for a new piece of hardware.

Nvidia’s colossal software organization lacked the foresight to take their massive advantage in ML hardware and software and become the default compiler for machine learning. Their lack of focus on usability is what enabled outsiders at OpenAI and Meta to create a software stack that is portable to other hardware. Why aren’t they the one building a « simplified » CUDA like Triton for ML researchers? Stuff like Flash Attention, why does it come out of Ph.D. students and not Nvidia?

The rest of this report will point out the specific hardware accelerator that has a huge win at Microsoft, as well as multiple companies’ hardware that is quickly being integrated into the PyTorch 2.0/OpenAI Trion software stack. Furthermore, it will share the opposing view as a defense of Nvidia’s moat/strength in the AI training market.

TorchInductor(トーチインダクター

TorchInductorは、複数のアクセラレータとバックエンドのための高速なコードを生成するpythonネイティブのディープラーニングコンパイラです。Inductorは、~250個の演算子を持つFXグラフを、~50個の演算子まで下げます。その後、Inductorはスケジューリングフェーズに移行し、演算子を融合させ、メモリ計画を決定する。

そして、CPUやGPUなどのAIアクセラレータ上で動作するコードを生成する「ラッパーコードジェン」へと移行する。ラッパーコードゲンは、コンパイラスタックのインタプリタ部分を置き換えるもので、カーネルの呼び出しやメモリの確保が可能です。バックエンドコード生成部は、GPU向けにはOpenAI Tritonを活用し、PTXコードを出力する。CPU向けには、IntelコンパイラがC++を生成します(Intel以外のCPUでも動作します)。

今後、さらに多くのハードウェアをサポートする予定ですが、重要なのは、Inductorによって、コンパイラチームがAIハードウェアアクセラレータ用のコンパイラを作成する際の作業量が劇的に減るということです。さらに、コードがより性能に最適化されます。メモリの帯域幅や容量の要件も大幅に削減されます。

私たちは、GPUだけをサポートするコンパイラを作りたくはありませんでした。C++と[OpenAI]Tritonを持つことで、その汎用性を強制することができるのです。

ジェイソン・アンセル - Meta AI

OpenAI Triton

OpenAIのTritonは、Nvidiaの機械学習のためのクローズドソースソフトウェアの堀に対して、非常に破壊的な角度を持っています。TritonはPythonを直接取り込むか、PyTorch Inductorスタックを介してフィードされます。後者が最も一般的な使用例でしょう。そして、Tritonは入力をLLVMの中間表現に変換し、コードを生成します。Nvidia GPUの場合、cuBLASなどのNvidiaのクローズドソースCUDAライブラリをスキップして、cutlassなどのオープンソースライブラリを優先し、直接PTXコードを生成します。

CUDAは、加速度計算を専門とする人たちにはよく使われていますが、機械学習の研究者やデータサイエンティストの間ではあまり知られていないようです。効率的に使うには難易度が高く、ハードウェアアーキテクチャを深く理解する必要があるため、開発プロセスが遅くなる可能性があります。そのため、機械学習の専門家は、コードの修正、最適化、並列化についてCUDAの専門家に頼ることがあります。

Tritonは、このギャップを埋めることで、より高いレベルの言語が、より低いレベルの言語を使用する場合と同等の性能を達成できるようにします。Tritonのカーネルは、一般的なML研究者にとって非常に読みやすく、ユーザビリティに優れています。Tritonは、SM内のメモリ合体、共有メモリ管理、スケジューリングを自動化します。Tritonは、すでに非常に効率的に行われている要素ごとの行列乗算には特に役に立ちません。Tritonは、コストのかかるポイントワイズ演算や、Flash Attentionのような複雑な演算で、より大きな融合演算の一部として行列乗算を行う場合のオーバーヘッドを削減するのに非常に有効です。

OpenAI Tritonは、現在Nvidia GPUのみを公式にサポートしていますが、それは近い将来変更される予定です。将来的には、他の複数のハードウェアベンダーがサポートされる予定で、このオープンソースプロジェクトは信じられないほどの勢いを増しています。他のハードウェアアクセラレータがTritonの一部であるLLVM IRに直接統合できるため、新しいハードウェア用のAIコンパイラスタックを構築する時間が劇的に短縮される。

Nvidiaの巨大なソフトウェア組織は、MLハードウェアとソフトウェアにおける巨大な優位性を活かし、機械学習のデフォルトコンパイラとなる先見性を欠いていた。Nvidiaがユーザビリティを重視していなかったからこそ、OpenAIやMetaの部外者が、他のハードウェアに移植可能なソフトウェアスタックを作ることができたのです。なぜ彼らは、ML研究者のためにTritonのような「簡略化された」CUDAを構築しないのでしょうか?フラッシュ・アテンションのようなものは、なぜNvidiaではなく、博士課程の学生から生まれるのか?

このレポートの残りの部分では、Microsoftで大成功を収めた特定のハードウェアアクセラレータと、PyTorch 2.0/OpenAI Trionソフトウェアスタックに迅速に統合されている複数の企業のハードウェアを指摘します。さらに、AIトレーニング市場におけるNvidiaの堀/強さの防御として、反対意見も共有する予定である。